Integrierte Memristor-basierte Rechnerarchitekturen

Das von der DFG geförderte Projekt IMBRA beschäftigt sich mit der Nutzung von Memristoren für Multibit-Register in einer RISC-V Befehlssatz-kompatiblen Prozessorarchitektur. Als technologische Basis werden konkret Resistive RAMs von IHP – Innovations for High Performance Microelectronics – Leibniz-Institut für innovative Mikroelektronik, eingesetzt.

Speziell geht es darum, den qualitativen Vorteil dieser Speichertechnologie, nämlich die Fähigkeit, mehr als zwei Zustände in einer physikalischen Zelle zu speichern, für den Einsatz in zukünftigen ternären Rechenwerken zu erforschen. Ternäre Rechenwerke bauen im Gegensatz zu binären Rechenwerken darauf, dass pro Ziffer in der Darstellung der Operanden nicht nur zwei Zustände (0 und 1), sondern drei Zustände verwendet werden, entweder -1, 0, und 1 bei vorzeichenbehafteter Zahlendarstellung oder 0, 1 und 2 für eine Darstellung mit expliziter Übertragsspeicherung. Ternäre Rechenwerke haben gegenüber binären den Vorteil einer unabhängig von der Wortlänge konstanten Laufzeit für die Addition und Subtraktion. In der Vergangenheit wurden u.a. solche ternären Rechenwerke nicht genutzt, da sie bei 1-Bit-Speicherzellen für die Register und für die Arbeitsspeicher eine Verdopplung der erforderlichen Speicherkapazitäten nach sich ziehen würden. Die Möglichkeit der neuen Speichertechnologien macht eine Neubewertung ternärer Rechenwerke erforderlich.

In IMBRA selbst werden dazu physikalische Modelle für Multibit-ReRAM-Zellen in IHP-Technologie auf Grundlage des Stanford-Modells für ReRAM-basierte Memristoren entwickelt, die zur Bewertung von Architekturalternativen in Simulationen verwendet werden. Ferner wurden verschiedene ternäre Zahlendarstellungen im Hinblick auf ihre Eignung für die Realisierung möglichst Energie-, Latenzzeit- und Chipflächen-minimaler Lösungen in aus CMOS-Logik und ReRAM-Multibit-Speicherzellen hybriden Schaltungen untersucht.

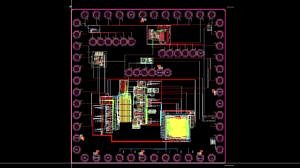

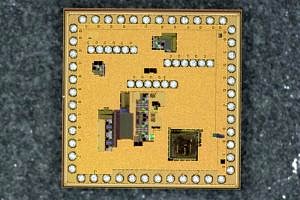

Bei der Umsetzung der ternären Rechenwerke wird ferner ein abgestuftes Vorgehen verfolgt. Zum einen werden Lösungen erarbeitet, in denen die Memristoren rein als ternäre Speicherzellen eingesetzt werden, d.h. nach erfolgter Analog/Digital Wandlung und Rückwandlung der Ergebnisoperanden werden sie dazwischen mit konventioneller digitaler CMOS-Logik verarbeitet. Dafür werden in IMBRA entsprechende Prototypen in IHP-Technologie umgesetzt. In einem weiteren Schritt wird zumindest auf der konzeptionell simulativen Ebene eine weitergehende Lösung verfolgt, welche die zusätzlichen Overhead verursachende AD- und DA-Wandlung vermeidet. In dieser schaltungstechnisch aufwendigeren Lösung wird im Sinne eines In-Memory-Computing-Ansatzes ein der ternären Addierlogik direkter Übergang der drei Zustände herbeigeführt.

IMBRA wird in Zusammenarbeit mit dem Lehrstuhl für Technische Elektronik der FAU (Prof. Robert Weigel) und dem Lehrstuhl für Kommunikationselektronik der Universität Bayreuth (Prof. Amelie Hagelauer) durchgeführt.

The DFG-funded project IMBRA („Integrated Memristor-based Computer Architectures“) deals with the use of memristors for multibit registers in a RISC-V instruction-set-compatible processor architecture. Specifically, resistive RAMs from IHP – Innovations for High Performance Microelectronics – Leibniz Institute for Innovative Microelectronics, are used as the technological basis.

In particular, the aim is to explore the qualitative advantage of this memory technology, namely the ability to store more than two states in one physical cell, for use in future ternary arithmetic units. In contrast to binary arithmetic units, ternary arithmetic units are based on the fact that not only two states (0 and 1) but three states are used per digit in the representation of the operands, either -1, 0 and 1 for signed-digit number representation or 0, 1 and 2 for a so-called stored-transfer-carry number representation. Compared to binary arithmetic units, ternary arithmetic units have the advantage of a constant run time for addition and subtraction independent of the word length. In the past, such ternary arithmetic units were not used, among other things, because they would entail a doubling of the required storage capacities for the registers and for the main memory since digitsal 1-bit memory cells have to be used. The emergence of the new memory technologies makes a re-evaluation of ternary arithmetic units necessary.

In IMBRA itself, physical models for multibit ReRAM cells in IHP technology based on the Stanford model for ReRAM-based memristors are being developed for the purpose to evaluate by simulations different architecture alternatives. Furthermore, various ternary number representations were investigated with regard to their suitability for realising the lowest possible energy, latency and chip area solutions in hybrid circuits consisting of CMOS logic and ReRAM multibit memory cells.

In the implementation of the ternary arithmetic units, a two-step approach is also being pursued. First, solutions are being developed in which the memristors are used purely as ternary memory cells, i.e. after analogue/digital conversion and reconversion of the result operands, their stored content is processed in between with conventional digital CMOS logic. For this purpose, corresponding prototypes are being implemented in IHP technology in IMBRA. Second, in a further step, a more advanced solution is being pursued, at least on the conceptual and simulative level, which avoids the additional overhead causing AD and DA conversion. In this solution, which requires more complex analogue circuitry, a direct transition of the three states is realized according to the rules of a ternary adder cell in the sense of an energy-saving in-memory computing approach.

Publikationen / Papers:

- Reuben, D. Fey, und C. Wenger, „A Modeling Methodology for Resistive RAM Based on Stanford-PKU Model With Extended Multilevel Capability“, IEEE Transactions on Nanotechnology, Bd. 18, S. 647–656, 2019, doi: 10.1109/TNANO.2019.2922838.

- Reuben und D. Fey, „A Time-based Sensing Scheme for Multi-level Cell (MLC) Resistive RAM“, in 2019 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC), Okt. 2019, S. 1–6, doi: 10.1109/NORCHIP.2019.8906921.

- Fritscher, J. Knödtel, M. Reichenbach, und D. Fey, „Simulating Memristive Systems in Mixed-Signal Mode using Commercial Design Tools“, S. 4, Nov. 2019, doi: https://doi.org/10.1109/ICECS46596.2019.8964856.

- Fey und J. Reuben, „Direct state transfer in MLC based memristive ReRAM devices for ternary computing“, in 2020 European Conference on Circuit Theory and Design (ECCTD), Sep. 2020, S. 1–5, doi: 10.1109/ECCTD49232.2020.9218323.