Experimental Setups

MathJax.Hub.Config({tex2jax: {inlineMath: [[‚$`‘,’`$‘], [‚\\(`‘,’`\\)‘]]}});

div.wp-caption img{padding: .5em;}

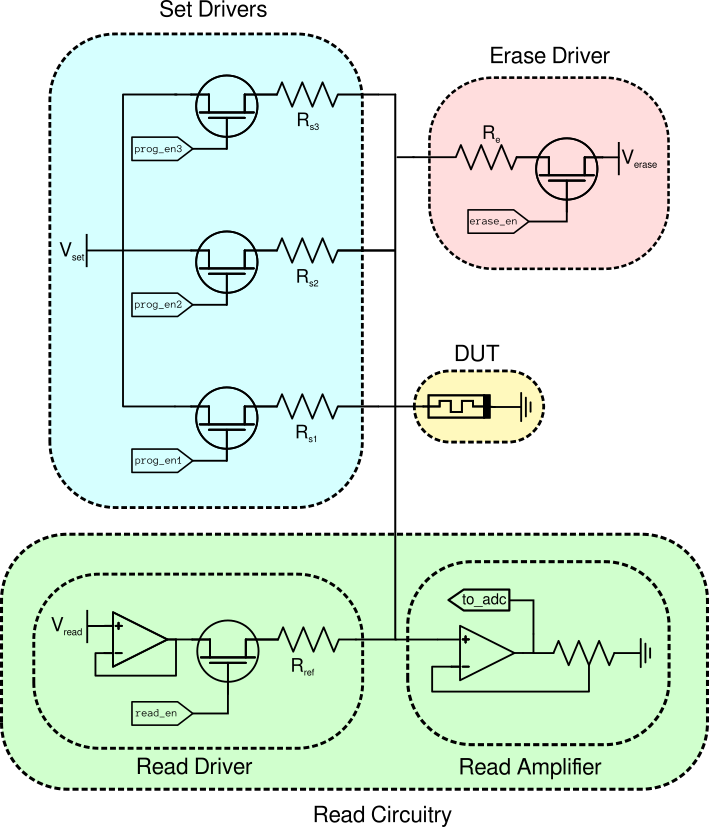

Since most researchers can not experiment with memristors embedded in their hardware, due to cost and technology issues, the memristors are attached as discrete devices (Figure 1c)). Using the setup we have implemented a small three-state register file and attached it to an implementation of the adder described in our article on redundant arithmetic.

- D. Wust, M. Biglari, J. Knödtel, M. Reichenbach, C. Söll and D. Fey, “Prototyping Memristors in Digital System with an FPGA-Based Testing Environment” International Workshop on Power And Timing Modeling, Optimization and Simulation (PATMOS) 2017, Thessaloniki, Greece, 2017, to be released in September↩